# Flow Latency Analysis with the Architecture Analysis and Design Language (AADL)

Peter Feiler

Jörgen Hansson

December 2007

**TECHNICAL NOTE**

CMU/SEI-2007-TN-010

**Performance-Critical Systems Initiative**

Unlimited distribution subject to the copyright.

This report was prepared for the

SEI Administrative Agent

ESC/XPK

5 Eglin Street

Hanscom AFB, MA 01731-2100

The ideas and findings in this report should not be construed as an official DoD position. It is published in the interest of scientific and technical information exchange.

This work is sponsored by the U.S. Department of Defense. The Software Engineering Institute is a federally funded research and development center sponsored by the U.S. Department of Defense.

Copyright 2007 Carnegie Mellon University.

**NO WARRANTY**

THIS CARNEGIE MELLON UNIVERSITY AND SOFTWARE ENGINEERING INSTITUTE MATERIAL IS FURNISHED ON AN "AS-IS" BASIS. CARNEGIE MELLON UNIVERSITY MAKES NO WARRANTIES OF ANY KIND, EITHER EXPRESSED OR IMPLIED, AS TO ANY MATTER INCLUDING, BUT NOT LIMITED TO, WARRANTY OF FITNESS FOR PURPOSE OR MERCHANTABILITY, EXCLUSIVITY, OR RESULTS OBTAINED FROM USE OF THE MATERIAL. CARNEGIE MELLON UNIVERSITY DOES NOT MAKE ANY WARRANTY OF ANY KIND WITH RESPECT TO FREEDOM FROM PATENT, TRADEMARK, OR COPYRIGHT INFRINGEMENT.

Use of any trademarks in this report is not intended in any way to infringe on the rights of the trademark holder.

Internal use. Permission to reproduce this document and to prepare derivative works from this document for internal use is granted, provided the copyright and "No Warranty" statements are included with all reproductions and derivative works.

External use. Requests for permission to reproduce this document or prepare derivative works of this document for external and commercial use should be addressed to the SEI Licensing Agent.

This work was created in the performance of Federal Government Contract Number FA8721-05-C-0003 with Carnegie Mellon University for the operation of the Software Engineering Institute, a federally funded research and development center. The Government of the United States has a royalty-free government-purpose license to use, duplicate, or disclose the work, in whole or in part and in any manner, and to have or permit others to do so, for government purposes pursuant to the copyright license under the clause at 252.227-7013.

For information about purchasing paper copies of SEI reports, please visit the publications portion of our Web site (<http://www.sei.cmu.edu/publications/pubweb.html>).

---

## Table of Contents

|                 |                                                         |           |

|-----------------|---------------------------------------------------------|-----------|

| <b>Abstract</b> | <b>vii</b>                                              |           |

| <b>1</b>        | <b>Introduction</b>                                     | <b>1</b>  |

| <b>2</b>        | <b>AADL Flow Specifications and Flow Instances</b>      | <b>4</b>  |

| 2.1             | Specification of Externally Visible Flows               | 4         |

| 2.2             | Flows Through Component Implementations                 | 5         |

| 2.3             | End-To-End Flows                                        | 6         |

| 2.4             | End-To-End Flow Instances                               | 7         |

| 2.5             | Textual Flow Declaration Examples                       | 8         |

| <b>3</b>        | <b>Latency Analysis Framework</b>                       | <b>10</b> |

| 3.1             | Processing Time                                         | 11        |

| 3.2             | Processing Delay                                        | 11        |

| 3.2.1           | Sampled Processing                                      | 12        |

| 3.2.2           | Synchronous and Asynchronous Sampling                   | 12        |

| 3.2.3           | Sampling of Processing Chains                           | 13        |

| 3.2.4           | Data-Driven Processing                                  | 14        |

| 3.3             | Transfer Time and Delay                                 | 15        |

| 3.4             | Use of Latency Property                                 | 15        |

| <b>4</b>        | <b>Latency Analysis Illustrated</b>                     | <b>17</b> |

| 4.1             | Thread-Level Instance Models                            | 17        |

| 4.2             | The Example Model                                       | 18        |

| 4.3             | Flow Processing Through Event Data Ports                | 19        |

| 4.3.1           | Data-Driven Processing through Queued Ports             | 19        |

| 4.3.2           | Sampled Data Stream Processing through Periodic Threads | 20        |

| 4.3.3           | Mixed Event Data Flow Processing                        | 22        |

| 4.3.4           | Harmonic Up and Down Sampling                           | 24        |

| 4.3.5           | Non-harmonic Sampling                                   | 25        |

| 4.4             | Flow Processing Through Data Ports                      | 25        |

| 4.4.1           | Use of Immediate Connections                            | 26        |

| 4.4.2           | Use of Delayed Connections                              | 26        |

| 4.4.3           | Mixing Immediate and Delayed Connections                | 27        |

| 4.4.4           | Data-Driven Processing of Data Ports                    | 29        |

| 4.5             | Use of Periodic Devices                                 | 29        |

| 4.6             | Communication Latency                                   | 29        |

| 4.7             | Partitioned Systems                                     | 29        |

| 4.8             | Multiple Fidelity Latency Analysis                      | 30        |

| <b>5</b>        | <b>The Flow Latency Analysis Plug-In</b>                | <b>32</b> |

| <b>6</b>        | <b>Summary</b>                                          | <b>34</b> |

| <b>Appendix</b> | <b>Example AADL Model</b>                               | <b>35</b> |

---

## List of Figures

|            |                                                                             |    |

|------------|-----------------------------------------------------------------------------|----|

| Figure 1:  | Flow Specifications for GPS System                                          | 5  |

| Figure 2:  | Flow Specification and Flow Implementation                                  | 5  |

| Figure 3:  | End-to-End Flow Declaration and Selection                                   | 6  |

| Figure 4:  | Flow Declarations and the System Hierarchy                                  | 7  |

| Figure 5:  | End-To-End Flow in a System Instance                                        | 8  |

| Figure 6:  | Asynchronous Sampling                                                       | 13 |

| Figure 7:  | Synchronous Sampling                                                        | 13 |

| Figure 8:  | Synchronously Sampled Processing Chain                                      | 14 |

| Figure 9:  | Timing of Immediate and Delayed Connections                                 | 14 |

| Figure 10: | Flow from a Sensor through Three Threads to an Actuator                     | 18 |

| Figure 11: | Data-Driven Flow Processing Chain                                           | 19 |

| Figure 12: | Synchronous Sampling Task Sequence                                          | 20 |

| Figure 13: | Harmonic Sampling                                                           | 24 |

| Figure 14: | The Effect on Latency of Mixing Immediate and Delayed Data Port Connections | 27 |

---

## List of Tables

|          |                                                                                 |    |

|----------|---------------------------------------------------------------------------------|----|

| Table 1: | Aspects of Defining Flow Specifications                                         | 9  |

| Table 2: | Determination of Values for Data-Driven Processing                              | 20 |

| Table 3: | Determination of Values for Sampled Data Stream Processing                      | 21 |

| Table 4: | Determination of Values for Mixed Event Data Flow Processing                    | 22 |

| Table 5: | Determination of Values for Harmonic Sampling                                   | 24 |

| Table 6: | Determination of Values Where Immediate Connections Are Used                    | 26 |

| Table 7: | Determination of Values Where Delayed Connections Are Used                      | 27 |

| Table 8: | Determination of Values Where T1 to T2 is Immediate and T2 to T3 is Delayed     | 28 |

| Table 9: | Determination of Values Where T1 Completion Triggers T2 and T2 to T3 is Delayed | 28 |

---

## Abstract

Control system components are sensitive to the end-to-end latency and age of signal data. They are also affected by variation (jitter) in latency and age values due to different runtime configurations (i.e., sampling or data-driven signal processing pipelines, dissimilar communication mechanisms, partitioned architectures, and globally synchronous versus asynchronous hardware). This technical note introduces an analysis framework designed to calculate the end-to-end latency and age of signal stream data as well as their jitter. The latency analysis framework and calculations are illustrated in the context of an example model that uses the flow specification notation of the Architecture Analysis & Design Language (AADL). The report describes how this latency analysis capability can be used to determine worst-case end-to-end latency on system models of different fidelity and how it accounts for partitioned architectures. It also summarizes the worst-case end-to-end flow latency analysis capability provided by the Open Source AADL Tool Environment (OSATE) flow latency analysis plug-in.

---

## 1 Introduction

Many embedded systems have control system components that process a signal data stream from sensors and affect the external environment (e.g., a physical plant) through actuators. The processing of such a signal stream is time sensitive. The degree of time sensitivity depends on the lag of the physical systems and the responsiveness of the control algorithm. It is also affected by the sampling age of the data (i.e., the amount of time expired since the data was read by a sensor and an output computed with this data is passed to an actuator).

Control algorithms are designed to accommodate this delay. However, control algorithms are sensitive to variation (jitter) in this delay. For example, Cervin, Årzén, and Henriksson describe how sampling jitter and end-to-end latency jitter from a sensor to an actuator affects the stability of controllers [Cervin 2006]. They also show that jitter varies according to the scheduling algorithm for executing a task set. In other words, the choice of runtime system affects end-to-end latency and age as well as their jitter. Their jitter is perceived by the control algorithm as increased noise in the data, which can occur when configuring an embedded application with different scheduling and communication policies or when migrating a proven legacy application to a new platform.

Furthermore, the end-to-end latency and the age of data in a signal stream may differ. End-to-end latency is the amount of time it takes for a new data value from a sensor to be processed and output at the actuator. If data elements are missing or the data stream is oversampled, the same data element may be processed multiple times. In that case, the age of the data output to the actuator may be larger than the end-to-end latency.

There are a number of contributors to the end-to-end latency/age and their jitter, including the following:

- actual execution time of a task

The execution time of a task can vary between a minimum and a maximum (or worst-case) time. Use of caches in processors may reduce the minimum execution time. But they may not reduce maximum execution time under worst-case assumptions, and preemption by another task may invalidate the cache, resulting in cache misses.

- completion time of a task

Other tasks and variation in their execution times affect the completion time of a task. That completion time may be later than its worst-case execution time due to other tasks sharing the processor or to synchronization on shared resources. The worst-case completion time of a task in a schedulable system is its deadline.

- sampling latency

Tasks may process a data stream in a data-driven manner (i.e., the completion of one task triggers the execution of the next task). In this case, any latency jitter due to tasks is cumulative. Control systems typically use sampling to process the data more deterministically and manage latency jitter. Sampling occurs at a given rate, is driven by a clock, and increases end-to-end latency.

- sampling jitter

Latency jitter may exceed the sampling period. In this case, the sampling task may process the old value sometimes and the new value other times. The mechanism used to communicate data between tasks may also contribute to sampling jitter. Communication through a shared data area may result in non-deterministic sampling when tasks execute preemptively on the same processor or concurrently on two different processor cores. For example, a task down-sampling at half the rate may sample two data elements in a row and then skip two data elements instead of sampling every other data element. This results in a sampling variation of two frames.

- globally asynchronous systems

In a globally synchronous system, task dispatches are aligned. As a result, the sampling latency can be determined by rounding the computational latency to the next multiple of the sampling rate. In a globally asynchronous system, the sampling latency has to be added to the computational latency to accommodate worst-case assumptions of misalignment of clocks. Furthermore, clock drift adds to latency jitter.

- partitioned architectures and time-triggered architectures

Partitioning is used to support integrated modular avionics (IMA). In order to achieve more deterministic behavior, frame-delayed communication is typically used. Frame-delayed communication limits increases in jitter, but it adds to end-to-end latency. Furthermore, frame-delayed communication may double the end-to-end latency in a migration to a partitioned system, when it is combined with an existing task communication mechanism such as periodic I/O through a high-priority task. Similarly, time-triggered architectures operate a deterministic protocol on a system bus to maintain deterministic behavior. Again, this may limit jitter and increase end-to-end latency.

The international, industry standard Architecture Analysis & Design Language (AADL) [SAE AS5506 2004] has the expressive power to model

- signal streams as end-to-end flows

- sampling and data-driven processing as periodic and aperiodic threads that communicate through sampling data ports and queued event data ports

- partitioned and time-triggered architectures

AADL also can map application software onto different hardware platforms and specify ranges of execution times on different platforms, deadlines, and expected latencies along specified data flows. Therefore, AADL models can form the basis for an analytical framework through which we can investigate the impact of the runtime system on end-to-end latency, age, and their jitter and compare those results against the assumptions made by the control algorithms.

In this report, we describe the ability of AADL to determine a lower bound for the worst-case end-to-end latency in a system. If this lower bound value exceeds the desired latency, the requirement is not met. The AADL model may reflect the actual system at different levels of fidelity. As the fidelity increases, the lower bound may increase as well, but it will never decrease. For example, we demonstrate that the end-to-end latency of a signal flow may be determined from a model at the level of subsystems that are mapped into partitions, where those partitions take into

account the latency due to cross-partition communication. The model may be refined to specify latency contributed by an individual subsystem due to processing, or the subsystem may be elaborated into a task model where execution times, deadlines, and sampling rates are taken into account. The application system may be mapped onto different hardware platforms; in that case, workload on individual processors and communication latency can be taken into account in the end-to-end latency analysis.

This technical note summarizes the flow latency analysis capabilities that are provided by the flow latency analysis plug-in for the Open Source AADL Tool Environment (OSATE). The flow latency analysis capability utilizes the ability of the AADL to support specification of end-to-end flows through a sequence of system components.

In Section 2, we describe the flow specification notation in AADL. In Section 3, we introduce a latency analysis framework for calculating the end-to-end latency, and in Section 4 we discuss its use on system models. In Section 5, we explain how the flow latency analysis plug-in can be used on system models of different fidelity.

---

## 2 AADL Flow Specifications and Flow Instances

A flow specification describes an externally observable flow of application logic through a component. Such logical flows may be realized through ports and connections of different data types and a combination of data, event, and event data ports. Flow specifications represent

- flow sources—flows originating from within a component

- flow sinks—flows ending within a component

- flow paths—flows through a component from its incoming ports to its outgoing ports

Flow instances describe actual flow sequences through components and sets of components across one or more connections. They are declared in component implementations. A flow sequence takes one of two forms:

1. A flow implementation describes how a flow specification of a component is realized in its component implementation.

2. An end-to-end flow specifies a flow that starts within one subcomponent and ends within another subcomponent.

Flow specifications, flow implementations, and end-to-end flows can have expected and actual values for flow-related properties (e.g., latency or rounding error accumulation).

The purpose of specifying end-to-end flows is to support various forms of flow analysis, such as end-to-end timing and latency, reliability, numerical error propagation, Quality of Service (QoS), and resource management based on operational flows. To support such analyses, relevant properties are provided for the end-to-end flow, the flow specifications of components, and the ports involved in the flow to be analyzed. For example, to deal with end-to-end latency, the end-to-end flow may have properties specifying its expected maximum latency and actual latency. In addition, ports on individual components may have flow-specific properties (e.g., an `in` port property specifies the expected latency of data relative to its sensor sampling time or in terms of end-to-end latency from sensor to actuator to reflect the latency assumption embedded in its extrapolation algorithm).

### 2.1 SPECIFICATION OF EXTERNALLY VISIBLE FLOWS

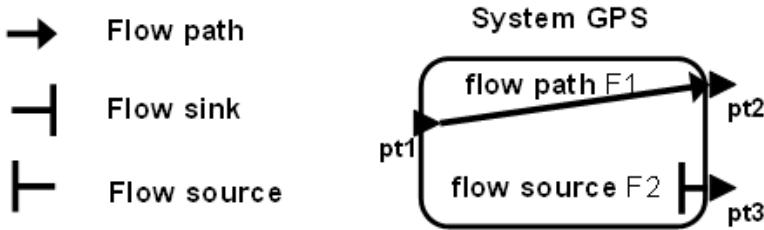

A flow specification declaration in a component type specifies an externally visible flow through a component's ports, port groups, or parameters. The flow through a component is called a flow path. A flow originating in a component is called a flow source. A flow ending in a component is called a flow sink. Figure 1 illustrates a system called *GPS* with three ports and two flow specifications. These are the flows through *GPS* and out of *GPS* that are externally visible. The flow path symbol is connected to two ports, while the flow source symbol is connected to one port.

Figure 1: Flow Specifications for GPS System

The ports identified by a flow specification can have different data and port types (i.e., one can be an event port and the other an event data port). Also, multiple flow specifications can be defined involving the same ports. For example, data coming in through an **in** port group is processed and data derived from one of the port group's contained ports is sent out through different **out** ports. This capability allows logical flows of information through components to be characterized by attributing flow specifications and the ports involved in flow specifications with relevant AADL property values. Properties other than the set of predeclared properties can be introduced through the AADL Property Set concept [Feiler 2006, p. 103].

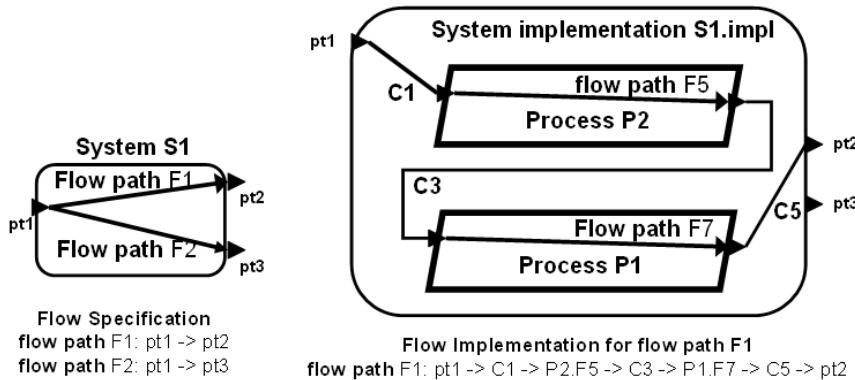

## 2.2 FLOWS THROUGH COMPONENT IMPLEMENTATIONS

A flow implementation declaration in a component implementation specifies how a flow specification is realized as a sequence of flows through subcomponents along connections from the flow specification **in** port to the flow specification **out** port. The system implementation for system *S1*, shown on the right of Figure 2, contains process subcomponents *P1* and *P2*. Each process subcomponent has two ports and a flow path specification as part of its process type declaration. The implementation of flow path *F1* is shown in both graphical and textual form on the right side of Figure 2. *F1* starts with port *pt1* and follows a sequence of connections and subcomponent flow specifications through connection *C1*, subcomponent flow specification *P2.F5*, connection *C3*, subcomponent flow specification *P1.F7*, and connection *C5*. This flow implementation ends with port *pt2*.

Figure 2: Flow Specification and Flow Implementation

Flow implementations can be declared for specific modes and mode transitions. Furthermore, flow implementations can have mode-specific property values, which accommodate the modeling of flows in modal systems. Once component implementations are known at multiple levels, actual flow properties such as latency at higher levels of the hierarchy can be calculated from the flow properties of the lower levels.

### 2.3 END-TO-END FLOWS

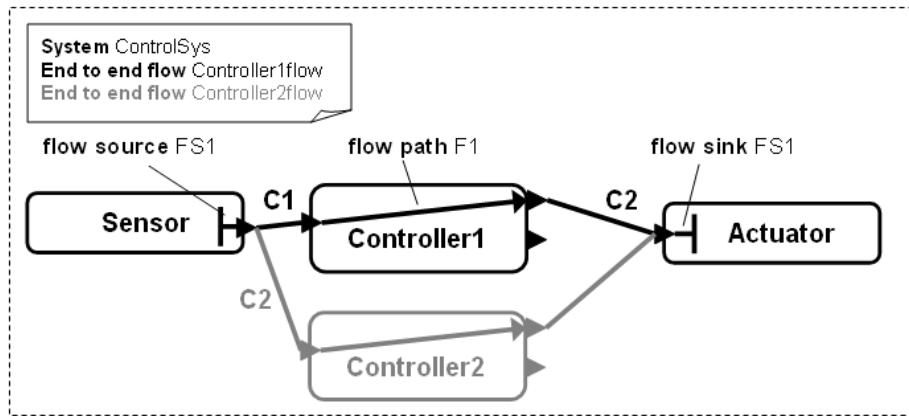

An end-to-end flow is a logical flow through a sequence of system components (i.e., threads, devices, and processors). An end-to-end flow is specified by an end-to-end flow declaration. End-to-end flow declarations are declared in component implementations, typically in the flow implementation in the system hierarchy that is the root of all threads, processors, and devices involved in an end-to-end flow. The subcomponent identified by the first subcomponent flow specification referenced in the end-to-end flow declaration contains the system component that is the starting point of the end-to-end flow. Subsequent named subcomponent flow specifications contain additional system components.

Figure 3 illustrates end-to-end flows of a system *ControlSys*. The selected end-to-end flow specification, *Controller1flow*, is shown in black, while the other one is shown in gray. The subcomponent flows and connections that make up the selected end-to-end flow are shown in black, while subcomponent flows and connections that are not part of the selected flow are shown in gray. An editor can use this visualization to display and support the definition of end-to-end flows. The user defines the elements of an end-to-end flow by selecting and deselecting subcomponent flows and connections. Flow implementations can be visualized in a similar manner.

Figure 3: End-to-End Flow Declaration and Selection

Notice that an end-to-end flow is expressed in terms of the flow specifications of its subcomponents. As a result, we can analyze flows in terms of subcomponent flow specifications without requiring the implementations of those components to be specified. We can validate the property values of a flow specification using the property values derived from the flow implementation that is based on the flow specification property values of its subcomponents. This capability supports a specification-based, low-fidelity analysis of architecture models early in the life cycle, before system details are available. As we refine a system architecture and provide a flow implementation for the refined components, the end-to-end flow analysis can be revisited at higher fidelity.

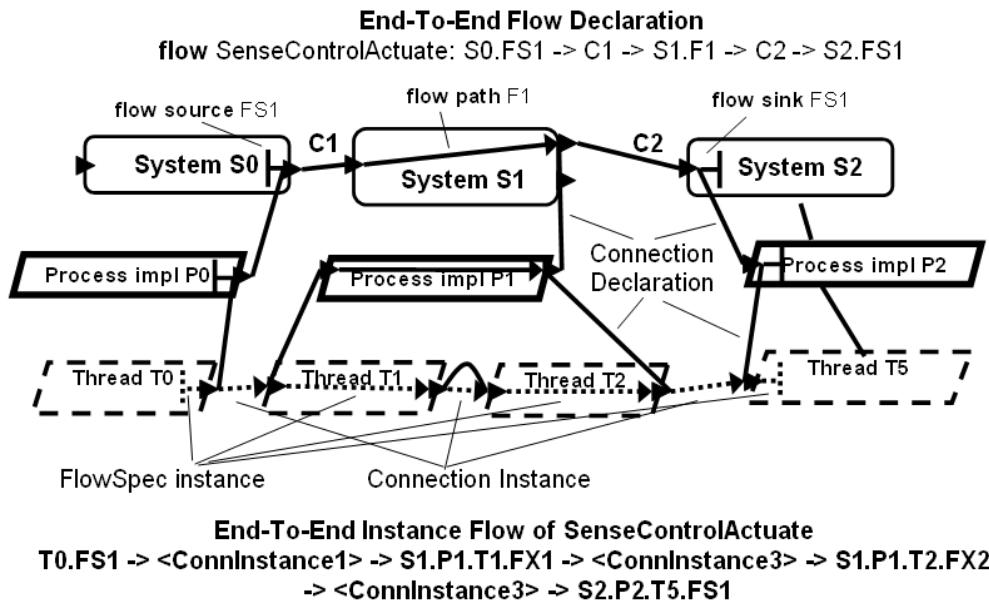

## 2.4 END-TO-END FLOW INSTANCES

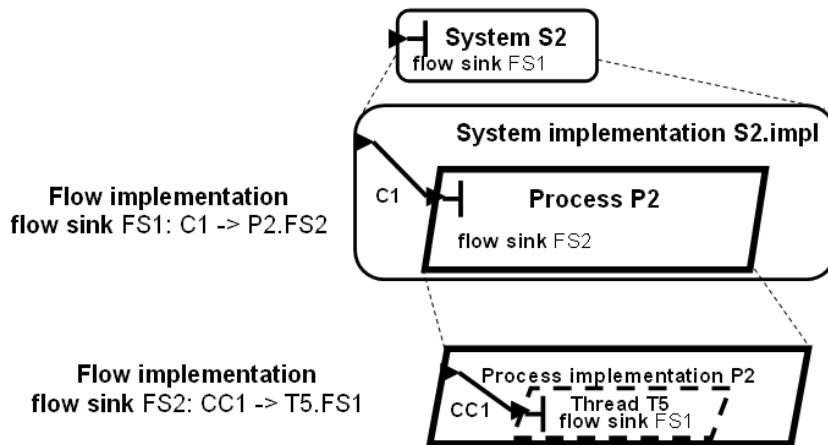

Flow declarations are associated with individual components. End-to-end flow declarations are specified in terms of the immediate subcomponents. For a system instance, these flow declarations are recursively expanded in the same way that subcomponent declarations result in a hierarchy of component instances in an AADL instance model or a collection of connection declarations results in a semantic connection.

Figure 4 shows how a flow sink specification expands into a three-level system hierarchy. The flow sink specification  $FS1$  for system  $S2$  is expanded into the connection  $C1$  and flow sink specification  $FS2$  of process  $P2$ , which in turn is expanded into the connection  $CC1$  and the flow sink specification  $FS1$  of thread  $T5$ . In short, the ultimate flow sink specification of system  $S2$  is the flow sink of thread  $T5$ .

Figure 4: Flow Declarations and the System Hierarchy

Figure 5 illustrates the expansion of an end-to-end flow declaration into the end-to-end instance flow in a system instance model. Notice that the end-to-end flow declaration is declared with the component implementation that is the common root of all system components involved with the end-to-end flow. In our example, the common root is the component implementation that contains systems  $S0$ ,  $S1$ , and  $S2$  as subcomponents. The ultimate flow source of the example end-to-end flow is the flow source in thread  $T0$ . The ultimate flow sink is the flow sink in thread  $T5$ . The end-to-end instance flow follows the semantic connections from thread  $T0$  to thread  $T1$ ,  $T1$  to  $T2$ , and  $T2$  to  $T5$ . Notice that the flow path  $F1$  of system  $S1$  represents the flow through both threads  $T1$  and  $T2$ . We have used dashed lines to mark the end-to-end instance flow in Figure 5.

Figure 5: End-To-End Flow in a System Instance

## 2.5 TEXTUAL FLOW DECLARATION EXAMPLES

The example in Table 1 illustrates various aspects of defining flow specifications. The **process** `foo` has several flow specifications. `Flow1` and `Flow2` are two different flow paths through the **process** from the same incoming port to two different outgoing ports. `Flow3` represents a flow where the **process** `foo` acts as an information sink (i.e., it consumes the **in event port** `initcmd`). Similarly, the **process** `foo` acts as an information source for the **out event port** `Status`.

The **process implementation** `foo.basic` consists of several threads that are assumed to have flow specifications as indicated in the commented text<sup>1</sup> and specifies a flow implementation for several flow specifications. This flow implementation indicates how the flow is realized as flow through the component's subcomponents. It also specifies two end-to-end flows that are local to the **process** `foo`: (1) ETE1 starts with a flow source of a subcomponent and ends with a flow sink of a different subcomponent, and (2) ETE2 specifies a flow whose starting and ending elements are flow paths (i.e., we are specifying a subflow of interest although the information flows in and out of the specified end-to-end flow).

<sup>1</sup> Comment lines in an AADL specification are prefaced by two dashes (--) .

Table 1: Aspects of Defining Flow Specifications

```

process foo

features

Initcmd: in event port;

Signal: in data port gps::signal_data;

Result1: out data port gps::position.radial;

Result2: out data port gps::position.cartesian;

Status: out event port;

flows

-- two flows split from the same input

Flow1: flow path signal -> result1;

Flow2: flow path signal -> result2;

-- An input is consumed by process foo through its initcmd port

Flow3: flow sink initcmd;

-- An output is generated (produced) by process foo and made

available

-- through its port Status;

Flow4: flow source Status;

end foo;

process implementation foo.basic

subcomponents

A: thread bar.basic;

-- bar has a flow path fs1 from p1 to p2

-- bar has a flow source fs2 to p3

C: thread baz.basic;

B: thread baz.basic;

-- baz has a flow path fs1

-- baz has a flow sink fsink

connections

conn1: data port signal -> A.p1;

conn2: data port B.p2 -> result1;

conn3: data port C.p2 -> result2;

conn4: data port A.p2 -> B.p1;

conn5: data port A.p2 -> C.p1;

conn6: event port A.p3 -> Status;

connToThread: event port initcmd -> C.reset;

flows

Flow1: flow path

signal -> conn1 -> A.fs1 -> conn4 ->

C.fs1 -> conn2 -> result1;

Flow2: flow path

signal -> conn1 -> A.fs1 -> conn5 ->

C.fs1 -> conn3 -> result2;

Flow3: flow sink initcmd -> connToThread -> C.fsink;

-- a flow source may start in a subcomponent,

-- i.e., the first named element is a flow source

Flow4: flow source A.fs2 -> connect6 -> status;

-- an end-to-end flow from a source to a sink

ETE1: end to end flow

A.fs2 -> conn5 -> C.fsink;

-- an end-to-end flow where the end points are not sources or

sinks

ETE2: end to end flow

A.fs1 -> conn5 -> C.fs1;

end foo.basic;

```

---

### 3 Latency Analysis Framework

Flow latency is the amount of time it takes for information to flow from the starting point of an end-to-end flow to its destination via connections and, possibly, intermediate components. The starting point, intermediate components, and destination can be threads or devices; we refer to them as tasks.

Flow latency is affected by these four factors:

1. processing time by tasks in the end-to-end flow

Tasks are AADL threads and devices.

2. processing delay due to queuing or sampling

Tasks may communicate via queued ports (AADL **event** or **event data** ports) or unqueued sampling ports (AADL **data** ports). The processing delay due to queuing is affected by the number of elements in the queue; the processing delay due to sampling is affected by the rate at which the information is being sampled.

3. transfer time of information between tasks along connections

Transfer between tasks may occur on the same processor (AADL threads bound to the same processor), between tasks on different processors, or between a task and a device. The transfer time is affected by the amount of data being transferred and the buses to which a connection is bound.

4. transfer delay due to queuing or waiting for time slots in the transfer protocol

Transfer delay due to queuing is affected by the number of elements in the transfer queue, while transfer delay due to time slotting is affected by the rate at which slots for transfer are made available by the transfer protocol.

The end-to-end latency of a flow is determined by the processing time of each task, processing delay by all but the first task, and transfer time and delay for each of the connections between the tasks.

We can distinguish between best-case latency and worst-case latency. Best-case latency is determined by the minimum execution time of each task involved in a flow. It establishes a lower bound under the assumption that each task can execute immediately (i.e., each task has dedicated or highest priority access to a processor and is not preempted by other tasks). Worst-case latency is determined by the deadline of each task involved in the flow under the assumption that the tasks are schedulable. It establishes a lower bound that can be reduced by effectively dropping task deadlines while maintaining schedulability for a given periodic workload.

Latency jitter is determined by the completion time of each task. Completion time is affected by a variation in actual execution time between the minimum and maximum execution time and is bounded by the deadline under the assumption that the task set is schedulable. For a fixed workload, the maximum completion time may be lower than the specified deadline; for a varying workload, the deadline represents an upper bound under the assumption that all deadlines are met.

The age of data differs from latency, when data is re-sampled—as is the case when up-sampling occurs or there are missing data elements in the data stream (e.g., due to a missing sensor reading).

In the following sections, we look at each of these factors in more detail.

### 3.1 PROCESSING TIME

Tasks have several timing-related properties that reflect the processing time, including the following:

- minimum and maximum execution time

Execution time, the amount of time the task is executing on a processor, is determined by the number of instructions executed. Therefore, execution time is dependent on processor speed and is affected by cache and pipelining techniques used by the processor. The minimum execution time can be used to determine a lower bound on latency, on the assumption that the active component is not preempted. The maximum execution time can be used to determine a lower bound on throughput, on the assumption that the active component is not preempted. `Compute_Execution_Time` plus `Recover_Execution_Time` properties in AADL specify a time range to represent these values. Processor-specific property values can be used to identify processor-type execution times. Alternatively, the execution time can be specified with respect to a reference processor, and a scaling factor for a specific processor type is used to determine the execution time.

- completion time and deadline

Completion time is the amount of time that expires between the dispatch and completion of a task. This time takes into account delays due to preemption or resource locking. The minimum completion time is the minimum execution time, under the assumption that the task execution is not delayed. Consequently, the minimum completion time is affected by the processor speed. The maximum completion time is the task deadline; it is not sensitive to the processor speed. The task deadline can be used to determine the maximum latency due to processing, on the assumption that the task set is schedulable. The `Deadline` property in AADL specifies the deadline for periodic, aperiodic, sporadic, and background threads.

For worst-case flow latency analysis, the AADL properties `Deadline` and `Period` are used. `Compute_Execution_Time` and `Recover_Execution_Time` are not utilized in the worst-case flow latency analysis. The lower bound of the `Compute_Execution_Time` represents the minimum execution time and a lowest bound for best-case end-to-end latency calculations.

### 3.2 PROCESSING DELAY

Several factors can cause processing delay. We examine these factors separately for sampled processing and data-driven (queued) processing.

### 3.2.1 Sampled Processing

Sampled processing occurs when a task is dispatched independently of the arrival of the input that is processed by the task.

A periodic task may sample the input on its incoming data ports at the rate of its period. Periodic tasks may also sample event ports and event data ports at the rate of their period. The sampling rate is determined by the rate at which a task is dispatched. For periodic threads (Dispatch\_Protocol property value Periodic) or devices with periodic drivers (Device\_Dispatch\_Protocol property value Periodic), the sampling delay is the value of the Period property.

At each sampling point, the task may process the complete port queue, if the Dequeue\_Protocol property value is AllItems (the default value), or it may process one item if the value is OneItem. A sampled processing thread may represent, for instance, a system health monitor that samples an alarm queue (event port) periodically. Note that if the arrival rate on an event data port is higher than the processing rate and only one item at a time is processed, the queue will routinely overflow, and data elements will be lost.

An aperiodic or a sporadic thread may sample the input on its incoming data ports if its dispatch is triggered by event or event data arrival that is not part of the flow being analyzed. The maximum interarrival rate determines the worst-case latency.

When an aperiodic or a sporadic thread is dispatched by the arrival of an event or event data from its predecessor in the flow, we have queued processing (see Section 3.2.4). When a data port processes by an aperiodic thread at the completion of its predecessor, it does not introduce processing delay. Instead, we have a processing chain (see Section 3.2.3).

### 3.2.2 Synchronous and Asynchronous Sampling

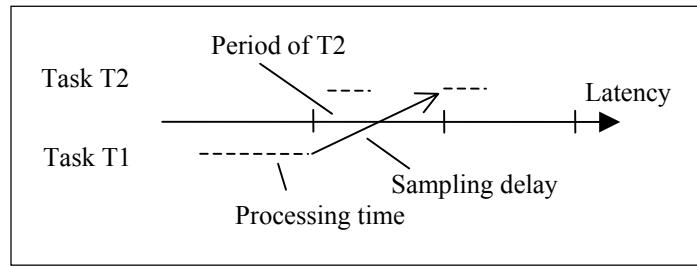

We can distinguish between scenarios where sampling dispatches of the predecessor and a given task are performed with respect to a common clock (synchronous sampling) and those where the task dispatch is performed independently (asynchronous sampling).

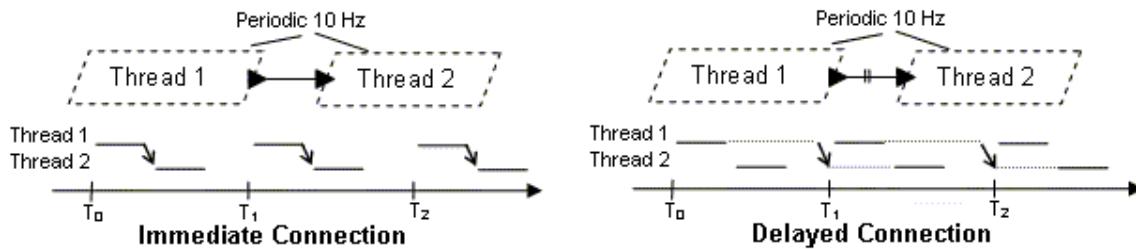

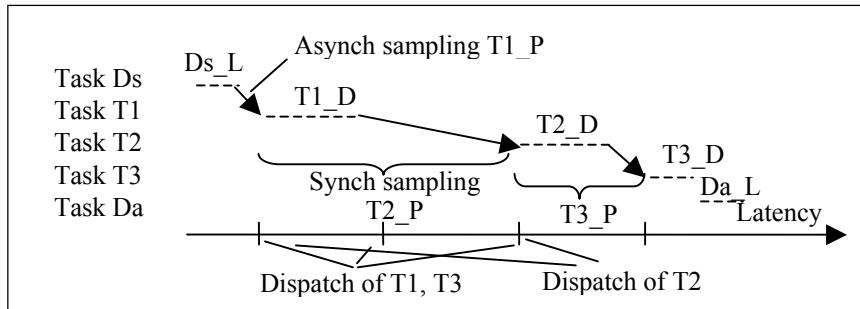

In asynchronous dispatch, the dispatch rate of the sampling task determines the processing delay. A sampling task dispatch may have just missed the arrival of the output, since the output is made available independently. This circumstance results in a maximum delay of the period between dispatches of the sampling task. Figure 6 shows a periodic task  $T_2$  that samples the output of an independently executing task  $T_1$ . The maximum processing delay due to sampling is the period of  $T_2$ , which is added to the processing time of  $T_1$  to determine the latency.

Figure 6: *Asynchronous Sampling*

This assumption is also the default interpretation in the AADL standard document. The AADL algorithm can easily be changed to handle globally asynchronous systems, in which each processor operates with a separate clock, or partially synchronous systems where some hardware components share clocks.

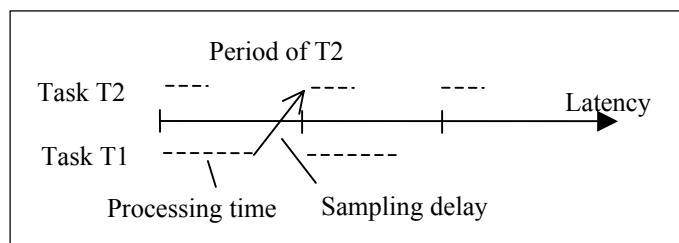

Synchronous sampling can occur for periodic threads on the same processor and on processors and devices whose execution is coordinated by a common clock. Synchronous sampling offers a more precise figure for worst-case latency by recognizing that the execution of several tasks occurs according to a common timeline. In that situation, the originator and the sampling task are dispatched periodically and their periods are harmonic (i.e., their periods are the same or one is a multiple of the other).

Figure 7 illustrates synchronous sampling for two tasks with the same period. The time of arrival of data at the sampling task  $T_2$  is the processing time of the originator  $T_1$  and any transfer time and delay. The processing delay of the sampling task is the difference between the arrival of data from the synchronous predecessor and the next dispatch time of the sampling task. The latency, which is the sum of the processing time of the predecessor and the processing delay of the sampling task, is the period of  $T_2$ .

Figure 7: *Synchronous Sampling*

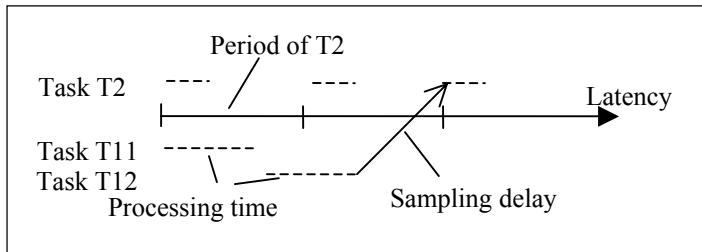

### 3.2.3 Sampling of Processing Chains

In general, the latency for synchronous sampling is the processing time plus any transfer time and delay rounded up to the next multiple of the sampling period. A periodic task may synchronously sample a processing chain that starts with a periodic task and has intermediate tasks whose dispatch is triggered by the completion of their predecessors—such as aperiodic threads or periodic threads with immediate data port connections. In this scenario, the cumulative time to be rounded

up is the sum of the processing times, any queued processing delays, and any transfer time and delays. Figure 8 illustrates sampling of such a processing chain  $T11$  and  $T12$  resulting in a latency of two periods of  $T2$ .

Figure 8: Synchronously Sampled Processing Chain

AADL supports data port connections with transfer timing characteristics that guarantee deterministic transfer of data streams. Data port connections can be declared to be immediate (mid-frame communication) or delayed (phase-delayed communication). We illustrate this capability in Figure 9. Delayed connections guarantee that the output of the originator is always sampled at the next dispatch of the active component, so that the processing delay is always the period of the receiver. Immediate connections delay the execution of the periodic recipient task, which effectively treats the periodic recipient as an aperiodic thread whose dispatch is triggered by the completion of the originator (i.e., a sampling processing chain).

Figure 9: Timing of Immediate and Delayed Connections

### 3.2.4 Data-Driven Processing

Data-driven processing occurs when transferred information drives the dispatch of a task, and the dispatch request is queued if the task has an active dispatch. These are aperiodic threads or devices whose dispatch is driven by input on an event or event data port. If an end-to-end flow includes events or event data through such ports, the queuing delay contributes to the end-to-end latency. Events or event data can be sent by a thread at any time during its execution. It is assumed that in the worst case, the event or event data was sent at completion time of the predecessor. In this case, under the assumption that the system is schedulable, the predecessor's deadline is its worst-case completion time.

The maximum processing delay is determined by the number of elements in the queue and the active dispatch. In other words, the worst-case processing delay is the queue size multiplied by the task deadline.

### 3.3 TRANSFER TIME AND DELAY

Transfer of information between tasks is affected by the size of the data, overhead of the transfer protocol, and speed of the execution platform component(s) that carry out the transfer. The size of data to be transferred is specified through the `Source_Data_Size` property, which can be associated with the `data` or `event data` port or with the `data` classifier of the `data` or `event data` port.

Transfers may occur within one processor or across processors through networks/buses. Thus, the transfer time is affected by the binding of the application components and connections to the execution platform. Transfer delay results from queuing within the transfer protocol implementation and multiplexing of the physical transfer medium.

Several properties have been predeclared in the AADL standard for buses and processors to determine the transfer time within memory or on a bus. The predeclared properties are `Assign_Time`, `Number_of_Bytes`, `Assign_Bit_Time`, and `Assign_Fixed_Time`. Using those properties, the equation for computing transfer time within memory or on a bus is as follows: ( $\text{Assign\_Time} = (\text{Number\_of\_Bytes} * \text{Assign\_Byte\_Time}) + \text{Assign\_Fixed\_Time}$ ).

The AADL standard also has predeclared a `Transmission_Time` and a `Propagation_Delay` time. `Transmission_Time` captures the amount of time it takes to transmit data. `Propagation_Delay` captures any delay in transmission due to the protocol used.

There may be situations where a hardware platform has not been identified or binding of tasks to processors has not been established. In these cases, the latency property associated with a connection is interpreted to take into account communication latency (see Section 4.6).

### 3.4 USE OF LATENCY PROPERTY

The AADL standard has three predeclared latency-related properties:

1. The `Latency` property can be specified for end-to-end flows, flow specifications, and connections. It represents the “maximum amount of elapsed time allowed between the time the data or [event] enters a flow or connection and the time it exits” [SAE AS5506 2004, p. 209].

2. The `Expected_Latency` property specifies “the expected latency for a flow specification” [SAE AS5506 2004, p.207].

3. The `Actual_Latency` property specifies “the actual latency as determined by the implementation of the end-to-end flow” [SAE AS5506 2004, p.189].

The flow latency analysis framework utilizes the `Latency` and `Expected_Latency` properties. When the analysis algorithm needs to retrieve a latency value, it first attempts to find the `Latency` value; if that value is not present, the algorithm attempts to retrieve the `Expected_Latency` value. The values can be used interchangeably, with the `Latency` value overriding the `Expected_Latency` value.

In a flow specification, the `Latency` (or `Expected_Latency`) property represents the flow latency that is expected to be contributed by the flow through the component. This value is used in end-to-end flow latency analysis as the latency value for each component of the instance model involved in the flow, unless the component is a thread or device and has its dispatch protocol, period, and deadline specified. If that is so, the latency determined by those property values is compared against the `Latency` value of the thread flow specification, and the smaller of the two is used in the end-to-end flow calculations. In other words, the `Latency` property value acts as a surrogate for the latency contribution by a component for which more detailed information for determining the latency contribution is not available.

In an end-to-end flow, the `Latency` (or `Expected_Latency`) property represents the latency value that the calculated end-to-end latency is compared against.

When flow latency analysis is applied to a declarative AADL model, the latency is computed for each flow implementation declaration and compared with the `Latency` (or `Expected_Latency`) property value of the flow specification.

A `Latency` (or `Expected_Latency`) property value can also be associated with a connection. This value is used in end-to-end flow latency analysis by default, unless the connection is bound to a bus. In that case, the computed latency value is determined by the transfer time and transfer delay based on the binding of the connection to execution platform components (bus, processor, and device)—as discussed in Section 3.3. This computed latency can be included in the flow latency analysis by redefining the `getConnectionLatency` method of the `FlowLatencyAnalysisSwitch` class to compute the latency for connection instances instead of retrieving the `Latency` or `Expected_Latency` value.

---

## 4 Latency Analysis Illustrated

In this section, we describe the calculation of end-to-end flow latency in the context of an example system to illustrate how sampling latency is determined for event and event data streams and periodic and aperiodic processing chains of threads that operate on signal streams (i.e., communicate state data through data ports). In a report on concurrency, Hansson and others provide a more formal treatment of bounds imposed by an application task and communication architecture on latency and other preference characteristics.<sup>2</sup>

For periodic and aperiodic processing chains, we can treat sequences of sampling periodic threads that are dispatched with respect to a common clock as special cases for which we can determine a less conservative latency value. We can distinguish between immediate and delayed connections and between periodic threads and devices. Furthermore, we can model periodic thread sampling with different periods (i.e., threads that down-sample or up-sample) as special cases by distinguishing between harmonic threads and non-harmonic threads.

For down-sampling by harmonic threads, the lower rate receiving thread does not sample and process every data element; thus, the latency of the skipped element does not have to be considered. In up-sampling, the same data element is sampled twice (i.e., the same data value is delivered more than once). For a new value, the end-to-end latency is determined by the first sample of the new value. This data value ages as it is repeatedly sampled. If aging due to up-sampling is to be taken into account in the latency calculation, the latency is determined by the longest period in the processing chain reduced by the amount of time the last thread in the chain finishes before the end of its period (i.e., the difference between that task's period and deadline).

In the following sections, we describe the instance model on which latency analysis is performed and introduce an example system model used in the illustration of the latency analysis. Then, we discuss modeling of the flow through event data ports with aperiodic threads (data-driven processing) and periodic threads (sampled processing). We discuss flows that are represented by data ports and periodic as well as aperiodic threads. We close this section with a discussion of latency contributions by partitioned system architectures and the ability to perform multifidelity latency analysis.

### 4.1 THREAD-LEVEL INSTANCE MODELS

Thread-level instance models are fully specified, with leaf components of the component instance hierarchy that are thread, device, processor, bus, and memory component instances. Communication between these components occurs through port connection instances. Port connection instances connect ports of leaf components in the instance hierarchy (e.g., from thread to thread, from device to thread, or thread to device). They represent a semantic connection, as defined in

---

<sup>2</sup> This report, *Impact of Architecture Concurrency on Performance Engineering* (CMU/SEI-2007-TN-048), is in development.

the AADL standard [SAE AS5506 2004]. A port connection instance (1) starts with a sequence of zero or more port mappings originating with a thread or device port, (2) makes a connection from one subcomponent port to another subcomponent port, and (3) ends with a sequence of zero or more port mappings from a component port to a port of one of its subcomponents. The port mappings and the subcomponent port connection are expressed by connection declarations in the component implementation that contains the subcomponent(s).

End-to-end flow instances consist of a sequence of `FlowSpec` instances of the leaf component instances involved in the flow and port connection instances that represent the flow between these leaf components. In an end-to-end flow instance, the typical sequence is as follows:

1. flow source instance

2. sequence of port connection instances and flow path instances of components in the end-to-end flow

3. port connection instance and a flow sink instance

Note that the starting and ending flow instances are not required to be flow sources and flow sinks; they can also be flow paths. This flexibility allows users to define end-to-end flows that are subsets of a complete end-to-end flow (e.g., define an end-to-end flow through the embedded software with inclusion of the flow through the sensor or actuator despite the flow of the first software component being a flow path that routes the input from a sensor to a component out port).

## 4.2 THE EXAMPLE MODEL

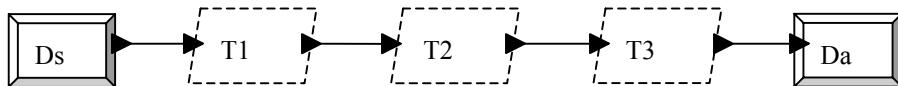

The system model in Figure 10 illustrates different aspects of the end-to-end flow analysis capability. In that figure, we present a system that consists of a sensor device *Ds*, two processes *P1* and *P2*, and an actuator device *Da*. Process *P1* consists of a single thread *T1*, while process *P2* consists of two threads *T2* and *T3*. We analyze end-to-end flows that start with *Ds*, flow through *T1*, *T2*, and *T3*, and end in *Da*. These flows may be represented by sampled **data** ports, or by queued **event data** ports. The devices and the threads may be dispatched periodically or aperiodically.

Figure 10: Flow from a Sensor through Three Threads to an Actuator

The three threads may execute on the same processor or on different processors. These processors may be connected by a bus, or they may operate with shared memory (e.g., dual-core processors). The distribution of the threads across processors may require them to be placed in separate processes. The resulting instance model is the same: port connection instances between thread instances.

The worst-case flow latency calculations described in this section represent a lower bound. In other words, distribution onto multiple processors may increase the latency due to communication. If

assumptions are made about a fixed periodic workload, the lower bound may be reduced by using the maximum completion time as the effective deadline, as discussed earlier.

### 4.3 FLOW PROCESSING THROUGH EVENT DATA PORTS

AADL offers event data ports to support queued data or message processing. The arrival of data on such a port can trigger the execution of an aperiodic thread, which is, in effect, data-driven processing. AADL also allows event data ports to be sampled by periodic threads. In this case, the thread may process one item in the queue or all items in the queue. In this section, we examine the impact of the data-driven and sampled flow representation on end-to-end latency.

A sensor device may observe an event in the physical environment and report the event through its port. This event is assumed to occur independently of any processing clock. An example of such a sensor is one that measures the rotation of a wheel. This type of sensor activity is modeled in AADL by an aperiodic device. A sensor device may also periodically sample the physical environment, such as measuring the temperature; this type is modeled in AADL by a periodic thread.

Similarly, an actuator device may react to the data arriving at its port (i.e., behave as an aperiodic thread). An example of this type of actuator is one that adjusts the angle of a flap. Alternatively, a device may operate periodically by sampling its input port. An example of such a device is a display that refreshes at a given rate.

In the next sections, we assume that the device is aperiodic. The effect of periodic devices on the latency calculation is addressed in Section 4.4.4. The Appendix includes a complete AADL model example with variations of system configurations that are concrete instances of the signal flow processing variations discussed in this section.

#### 4.3.1 Data-Driven Processing through Queued Ports

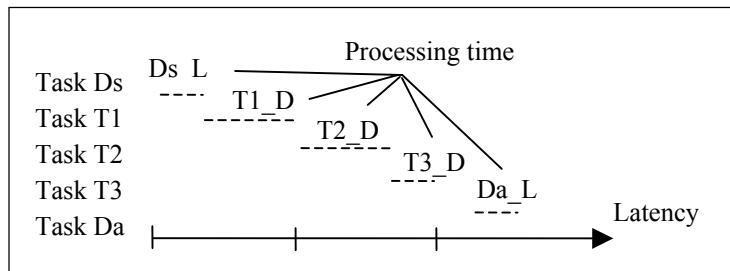

Data-driven processing is modeled in AADL by event data ports and aperiodic threads whose dispatch is triggered by the arrival of data. In the example shown in Figure 11, the devices and threads operate aperiodically. The sending of event data is triggered within the device  $D_s$ ; the arrival of event data triggers the execution of  $T_1$ , which in turn triggers  $T_2$ , followed by  $T_3$ . Completion of  $T_3$  triggers the execution of  $D_a$ .

We assume that  $D_s$  and  $D_a$  have specified a Latency ( $L$ ) property value for their flow specifications, while the threads have specified a Deadline ( $D$ ). Notice that the end-to-end flow is effectively a processing chain; its end-to-end latency is the cumulative worst-case completion time, which is the sum of the deadlines. Table 2 contains the details for latency and other values.

Figure 11: Data-Driven Flow Processing Chain

Table 2: Determination of Values for Data-Driven Processing

| Property                | Computation of Value                                                                                                                                                                           | Detail                                                                                                                                                                                                                                                                               |

|-------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Worst-case flow latency | The sum of $Ds\_L + T1\_D + T2\_D + T3\_D + Da\_L$                                                                                                                                             | If the event data ports have a queue greater than zero, the latency is increased by queuing delay, which in the worst case is QueueSize * D of the thread with the incoming port.                                                                                                    |

| Best-case flow latency  | The sum of $Ds\_L + T1\_P + T2\_P + T3\_P + T3\_Emin + Da\_L$ ( $Emin$ represents the minimum execution time), with the assumption that the queues are always empty                            | This lower bound increases as <ul style="list-style-type: none"> <li>faults occur and recovery execution time is added</li> <li>actual execution time ranges between the minimum and maximum values</li> <li>completion time increases due to preemption by other threads</li> </ul> |

| Maximum latency jitter  | The sum of <ul style="list-style-type: none"> <li>the difference between the minimum execution times and the deadlines of all threads</li> <li>the queuing latencies of all threads</li> </ul> | This variation can be larger than the period of an individual processing step (frame).                                                                                                                                                                                               |

| Age of data             | Same as its latency                                                                                                                                                                            |                                                                                                                                                                                                                                                                                      |

| Output                  | Data-driven                                                                                                                                                                                    | Missing input results in missing output.                                                                                                                                                                                                                                             |

### Observations

- If a thread has a specified flow specification latency, this latency is expected not to exceed the deadline of the thread. If a flow latency smaller than the deadline can be guaranteed, it is effectively the deadline of the thread and assures schedulability; that flow latency can be used in the calculation.

- All sensor readings are processed by all processing steps unless a port queue overflows. Missed or dropped sensor readings result in a missed output in the end-to-end flow.

#### 4.3.2 Sampled Data Stream Processing through Periodic Threads

Event data ports that are sampled by periodic threads can be used to represent applications such as a health monitor that periodically monitors event, alarm, or message streams without creating overload conditions (due to high burst alarm) or message rates (by not reacting to every arriving event or event data individually). In a sampled data stream, the thread is assumed to examine all items in the port queue on dispatch.

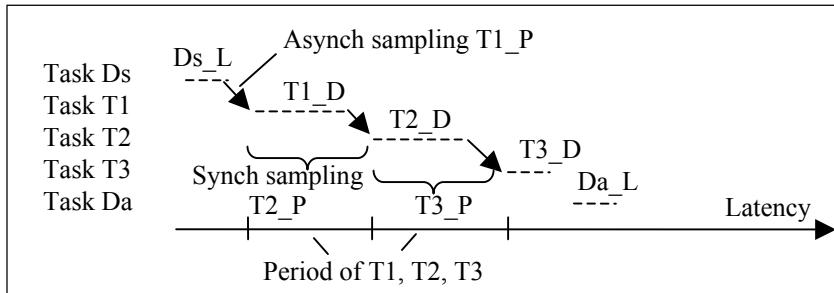

Figure 12: Synchronous Sampling Task Sequence

In the example shown in Figure 12, the devices operate aperiodically, while the threads periodically sample the flow through event data ports. The threads may sample with the same rate (pe-

riod) or different rates. Table 3 contains the computations and details for latency and other values for synchronous and asynchronous sampling.

*Table 3: Determination of Values for Sampled Data Stream Processing*

| Property                                                                                          | Computation of Value                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Detail                                                                                                                                                                                                             |

|---------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <b>Synchronous sampling (with all sampling at same rate)</b>                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                    |

| Worst-case flow latency                                                                           | The sum of $Ds\_L + T1\_P + T2\_P + T3\_P + T3\_D + Da\_L$                                                                                                                                                                                                                                                                                                                                                                                                                    | For $T2$ and $T3$ , the sampling delay $Ti\_P$ is assumed to be larger than or equal to $Ti\_D$ if all the periods are equal and the deadline is less than or equal to the period.                                 |

| Best-case flow latency                                                                            | The sum of $Ds\_L + T1\_P + T2\_P + T3\_P + T3\_Emin + Da\_L$ ( $Emin$ represents the minimum execution time.)                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                    |

| Maximum latency jitter                                                                            | The difference between the minimum execution time and the deadline of $T3$                                                                                                                                                                                                                                                                                                                                                                                                    | The jitter is less than the period of $T3$ .                                                                                                                                                                       |

| Age of data                                                                                       | The same as the latency unless an element is missing in the data stream. For each set of consecutively missing elements, the age increases by the time interval since the last real value of the component that drops a data stream element. For example, if a sensor operates at a rate of 10 ms, a missed reading adds 10ms. If the computation of $T2$ operates at 20 ms and cannot produce output in time, 20 ms are added to the age of the data passed to the actuator. | There is no increase in age due to up-sampling in this scenario, as the threads are assumed to have the same period. Missed elements may be due to the sensor or any of the processing steps not producing output. |

| Output                                                                                            | Produced with every period                                                                                                                                                                                                                                                                                                                                                                                                                                                    | It may be based on aged data.                                                                                                                                                                                      |

| <b>Asynchronous sampling (the dispatch of different threads is triggered by different clocks)</b> |                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                    |

| Worst-case flow latency                                                                           | The sum of $Ds\_L + T1\_P + T1\_D + T2\_P + T2\_D + T3\_P + T3\_D + Da\_L$                                                                                                                                                                                                                                                                                                                                                                                                    | Clocks may be offset from each other and have drift. The maximum offset equals the period; thus, we add the sampling period to the processing time of the predecessor.                                             |

| Best-case flow latency                                                                            | The sum of $Ds\_L + T1\_P + T1\_Emin + T2\_P + T2\_Emin + T3\_P + T3\_Emin + Da\_L$ ( $Emin$ represents the minimum execution time.)                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                    |

| Maximum latency jitter                                                                            | The sum of the differences between the minimum execution time and the deadline of each thread                                                                                                                                                                                                                                                                                                                                                                                 | It may exceed one or more frames.                                                                                                                                                                                  |

| Age of data                                                                                       | The same as the latency unless an element is missing in the data stream (see synchronous case)                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                    |

| Output                                                                                            | Produced with every period of $T3$                                                                                                                                                                                                                                                                                                                                                                                                                                            | It may be based on aged data.                                                                                                                                                                                      |

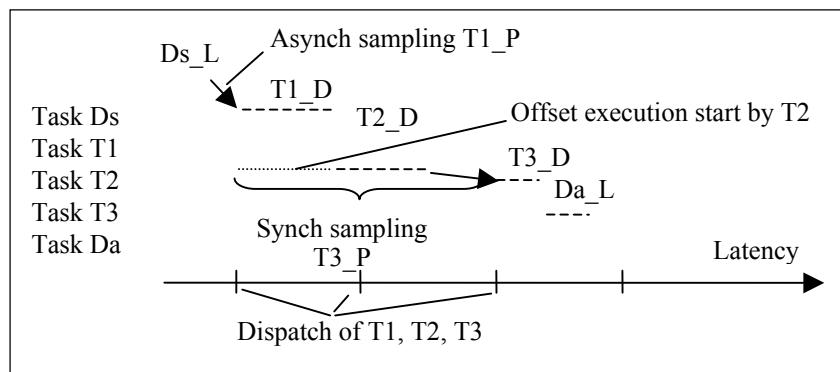

### 4.3.3 Mixed Event Data Flow Processing

In mixed event data flow processing, the devices operate aperiodically. Processing is a combination of sampled and data-driven operations. The threads, therefore, are a combination of aperiodic and periodic threads. In our example, we describe two scenarios:

1. The first thread ( $T1$ ) is aperiodic; the second ( $T2$ ), periodic; and the third ( $T3$ ), aperiodic.

The cumulative processing time of the sensor device  $Ds$  and the thread  $T1$  is sampled by the thread  $T2$ . This sampling is asynchronous because it is the first sampling in the flow. The processing times of  $T2$ ,  $T3$ , and the actuator device  $Da$  are cumulative and add to the total latency.

2. Threads  $T1$  and  $T3$  are periodic, while thread  $T2$  is aperiodic.

$T1$  performs asynchronous sampling of the  $Ds$  processing time. The cumulative processing time of  $T1$  and  $T2$  is sampled by  $T3$ . This sampling is synchronous with respect to the period of  $T1$ .

Table 4 contains the computations and details for latency and other values.

*Table 4: Determination of Values for Mixed Event Data Flow Processing*

| Property                                                                                                | Computation of Value                                                                                                                                                                                                                         | Detail                                                                                                                                     |

|---------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------|

| <b>Sampling where <math>T1</math> and <math>T3</math> are aperiodic and <math>T2</math> is periodic</b> |                                                                                                                                                                                                                                              |                                                                                                                                            |

| Worst-case flow latency                                                                                 | The sum of $Ds\_L + T1\_Emin + T2\_P + T2\_Emin + T3\_Emin + Da\_L$                                                                                                                                                                          | $T2$ is the first thread to sample the flow, thus, its sampling occurs independently (asynchronously) to the device generating the stream. |

| Best-case flow latency                                                                                  | The sum of $Ds\_L + T1\_Emin + T2\_P + T2\_Emin + T3\_Emin + Da\_L$ ( $Emin$ represents the minimum execution time.)                                                                                                                         |                                                                                                                                            |

| Maximum latency jitter                                                                                  | The sum of differences between the minimum execution time and the deadline of $T1$ , $T2$ , and $T3$                                                                                                                                         | It may exceed one or more frames.                                                                                                          |

| Age of data                                                                                             | The same as the latency unless an element is missing in the data stream. For each set of consecutively missing elements, the age increases by the time interval since the last real value of the component that drops a data stream element. | Missed elements may be due to the sensor or any of the processing steps not producing output (e.g., due to missed deadline).               |

| Output                                                                                                  | Produced with every period                                                                                                                                                                                                                   | It may be based on aged data.                                                                                                              |

Table 4: Determination of Values for Mixed Event Data Flow Processing (cont.)

| Property                                                                      | Computation of Value                                                                                                                                                                                                                          | Detail                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|-------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|